June 17, 2021

Best demo paper award

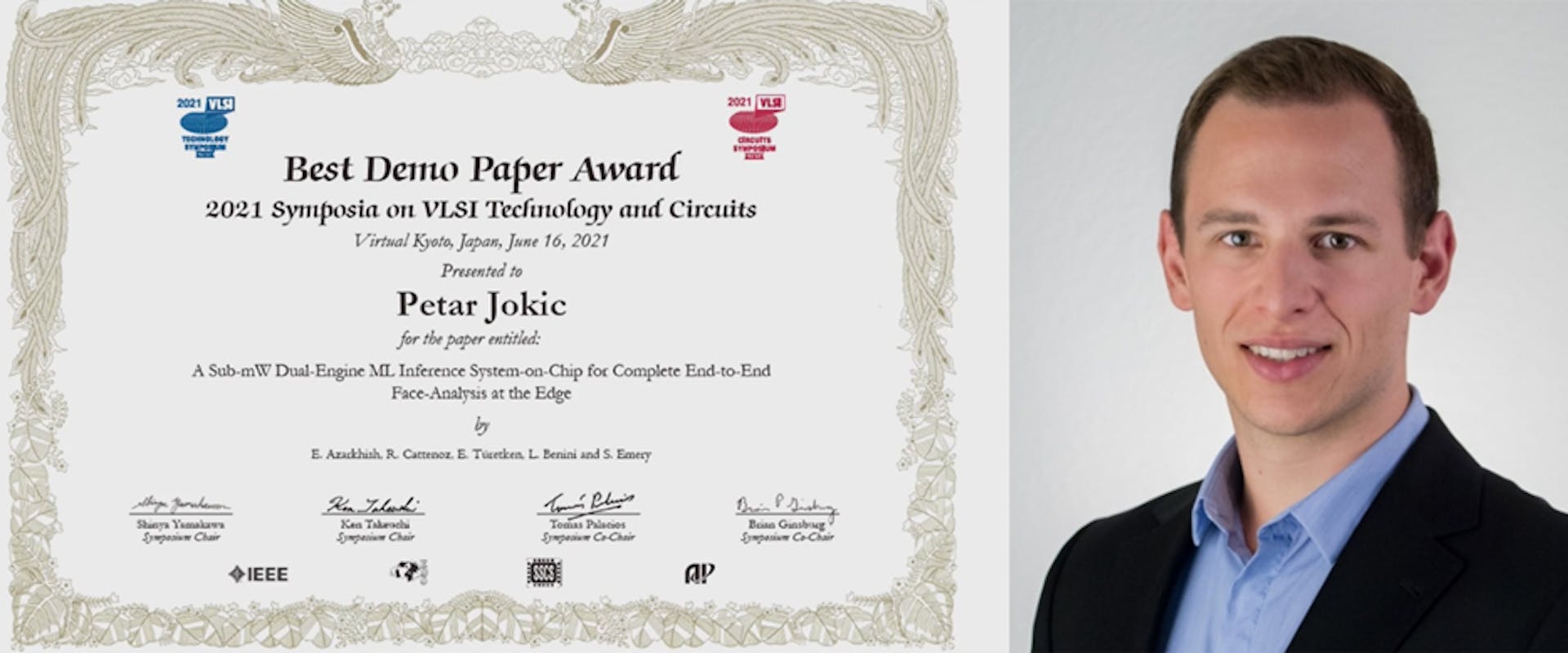

The international symposium on VLSI Technology and Circuits has awarded CSEM’s Petar Jokic and his co-authors a Best Demo Paper award for their work entitled “A Sub-mW Dual-Engine ML Inference System-on-Chip for Complete End-to-End Face-Analysis at the Edge.” The award was presented (virtually) on June 17, 2021, in Kyoto, Japan.